Badania właściwości tranzystorów w stanach dynamicznych sprowadzają się do szeregu pomiarów, których wyniki decydują o możliwościach stosowania tych tranzystorów w urządzeniach przemysłowych. Na stany dynamiczne tranzystora (włączenie, wyłączenie) wpływa szereg parametrów zewnętrznych takich jak: wartość napięcia bramki UGS, opornika bramkowego RG , temperatura, oraz napięcie UDS na tranzystorze w czasie jego blokowania i wartość prądu przewodzonego ID przez tranzystor.

Rys. 4. Metodologia pomiaru - przebieg prądu ID i napięcia UDS oraz przebiegi dodatkowe M1 (moc) i M3 (całka mocy).

Dla powyższych parametrów przeprowadzone zostały kolejne rejestracje prądu i napięcia dokonane za pomocą oscyloskopu na podstawie których sporządzono odpowiednie wykresy. Rejestrowane były tylko dwie wartości przebiegów napięcia UDS i prądu ID.Dodatkowe przebiegi takie jak moc (UDS*ID), oraz całka tej mocy (energia) charakteryzujące właściwości dynamiczne tranzystora zostały obliczone na podstawie chwilowych wartości prądu i napięcia. Na rysunku 4 przedstawione są wspomniane przebiegi wraz z wyliczonymi wartościami (dolna środkowa część rysunku) na podstawie których wyznaczono poszczególne charakterystyki.

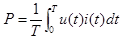

Głównym parametrem jaki był wyliczany była energia, która jest wprost proporcjonalna do mocy P i czasu t co przedstawia zależność (2). W przypadku przebiegu zmiennego w czasie , moc jest całką iloczynu napięcia i prądu w okresie T, wyrażoną wzorem (3). W odniesieniu do rysunku 4 energia włączenia lub wyłączenia tranzystora jest wyliczana z całki mocy wydzielonej w czasie (t2 - t1). Kursory a(t1) i b(t2) przecinają przebieg UDS odpowiednio w 90% i 10% wartości tego napięcia.

| (2) |

| (3) |

Pierwszym badaniom jakim został poddany tranzystor był wpływ wartości napięcia UGS załączania tranzystora na wartość energii załączania EON i wyłączania EOFF tranzystora. Na rysunku 5 przedstawiony jest schemat sterownika z uwzględnieniem regulacji napięcia stałego V1 w zakresie od 15V do 21V i w takim zakresie przeprowadzono pomiary.

Rys. 5. Schemat sterownika tranzystora z uwzględnieniem regulowanego napięcia dodatniego włączenia tranzystora V1(UGS)

Badanie wykonano dla stałego napięcia emiter-collector VDC=600V (rys.1), prąd ID (ang. Continous Drain Current) równy 20A, oraz wartość opornika bramkowego (rys.5) wynosząca 5Ω. Wyniki są przedstawione na rysunku 6.

Rys. 6. Wykres zależności energii (a) i czasów (b) w stanach dynamicznych w funkcji wartości napięcia dodatniego włączenia tranzystora UGS

Z wykresu a) wynika, że minimalną energię włączenia osiągnięto przy napięciu bramki 20V. Taką wartość rekomenduje producent. Wartość napięcia bramki ma wpływ także na czasy narastania i opadania napięcia blokowania tranzystora, co obrazuje wykres b) (rys. 6).

Kolejno przeprowadzono badanie wpływu wartości prądu drenu tranzystora na energię i czas włączenia i wyłączenia. Pomiary wykonano dla napięcia 600V przy dwóch wartościach opornika bramkowego RG=5Ω i RG=10Ω i napięciu UGS=20V. Zmiany wartości prądu uzyskano poprzez zmianę czasu narastania prądu w dławiku L1 (rys.2). Na rysunku 7 przedstawiono rezultaty pomiarów.

Rys. 7. Wykres zależności energii a), czasów b), piku prądu c) i średniej mocy d) w stanach dynamicznych w funkcji prądu drenu ID tranzystora.

Analizując powyższe rysunki zauważono, że straty łączeniowe tranzystora rosną proporcjonalnie wraz ze wzrostem prądu drenu i rezystancji opornika bramkowego (rys.7a). Czas opadania napięcia blokowania tfv podobnie jak energia rośnie wraz z wzrostem prądu drenu i napięciem blokowania tranzystora. Inaczej zachowuje się charakterystyka czasu narastania napięcia blokowania trv, ponieważ maleje nieliniowo i ustala się w zależności od rezystancji opornika bramkowego (rys. 7b). Zarejestrowane czasy nieznacznie odbiegają od czasów podanych w katalogu producenta firmy CREE [3]. Z (rys. 7c) wynika, że wartość szczytowa prądu drenu IDpeak w funkcji prądu drenu ID jest stała dla różnych wartości rezystancji opornika bramkowego. Rysunek 7d przedstawia wartość mocy jaka wydziela się w badanym przyrządzie półprzewodnikowym w stanach włączenia i wyłączenia. Średnia wartość strat mocy w stanach dynamicznych nieznacznie się zmienia w zależności od wartości rezystancji opornika bramkowego, ale się zmienia - wzrasta - , wraz ze wzrostem prądu drenu tranzystora.

Inną charakterystykę energii i czasów w funkcji napięcia blokowania ilustrują wykresy na rysunku 8. Charakterystyki były wyznaczone dla stałego prądu drenu równego 20A i dla dwóch wartości rezystancji bramkowej RG równej 5Ω i 10Ω. Z charakterystyk (rys.8) wynika, że energia w stanach dynamicznych rośnie wraz ze wzrostem napięcia UDS. Inaczej to wygląda jeśli spojrzymy na wykres z pomiarem czasów (rys.8b). Czas opadania (fall time) napięcia UDS podobnie jak energia rośnie wraz ze wzrostem napięcia blokowania i rezystancji opornika bramkowego.

Czas narastania (ang. rise time) napięcia UDS maleje wraz ze wzrostem napięcia blokowania i osiąga minimum przy napięciu 450V, a następnie zaczyna rosnąć. Na wykresach z rysunku 9 przedstawione są przebiegi czasowe prądu, napięcia, energii i mocy w stanach dynamicznych tranzystora dla badań w funkcji prądu drenu (charakterystyki z rys. 7).

Rys. 8. Wykres przebiegu energii a) i czasów b) w funkcji napięcia blokowania dla różnych wartości opornika bramkowego.

Rys. 9. Wykresy przebiegów czasowych prądu ID, napięcia UDS, energii E i mocy P w chwili włączenia a), b) i wyłączenia badanego tranzystora c), d) dla napięcia blokowania 600V

|

|

| REKLAMA |

| REKLAMA |