Obszary zastosowań modulatorów z asynchronicznym próbkowaniem, to np.: medyczne techniki obrazowania (tomografia komputerowa i rezonans magnetyczny, rejestracja sygnałów EKG i ogólnie zdalne nadzorowanie), rejestracja zakłóceń impulsowych w liniach energetycznych, czujniki i rejestratory stężenia gazów np. w kopalniach [1].

Istotną cechą metod kodowania różnicowego jest to, że uwalniając całkowitą informację źródła od redundancji i kodując jej pozostałą część, mogą silnie zmniejszać wymaganą liczbę bitów, czyli zwiększać kompresję. Algorytmy modulacji różnicowych w swym opisie funkcjonalnym są bardzo proste, co skłania ku ich bezpośredniej realizacji sprzętowej.

Modulatory ANS-DM (ang. Adaptive Nonuniform Sampling – Delta Modulation [2]), to przetworniki różnicowe 1-bitowe z adaptacją zarówno kroku kwantyzacji jak i częstotliwości próbkowania (NS-DM – to przetworniki różnicowe 1-bitowe z adaptacją jedynie częstotliwości próbkowania). Dzięki jednoczesnemu zmniejszaniu odstępu próbkowania τpi (i – kolejny moment próbkowania) i zwiększaniu kroku kwantyzacji qi koder ANS-DM charakteryzuje się dużą szybkością zmian sygnału aproksymującego, przy stosunkowo niewielkim zakresie zmian każdego z adaptowanych parametrów. Zmniejsza to szumy przeciążenia stromości przez ograniczenie przeregulowań [3], zapewniając, wypadkowo wzrost SNR co jest szczególnie istotne przy konwersji analogowych sygnałów niestacjonarnych. Pojawiające się w przetwarzanym sygnale składowe wolnozmienne prowadzą do zmniejszenia odstępów między kolejnymi momentami próbkowania i kroku kwantyzacji, a to z kolei redukuje szum granulacji i średnią przepływność bitową [2, 3].

Rys. 1. Schematy blokowe: a) modulator ANS-DM, b) demodulator ANS-DM

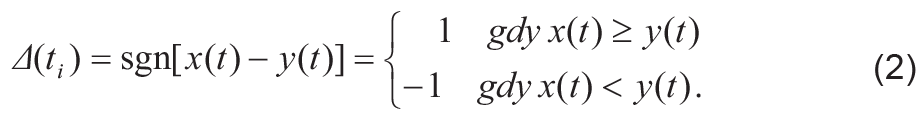

Zgodnie ze schematem blokowym modulacji ANS-DM, (rys. 1) analogowy sygnał wejściowy x(t) porównywany jest z sygnałem aproksymującym y(t), którego wielkość na wyjściu predyktora w chwilach próbkowania ti wynosi:

Operacja kwantowania, podobnie jak w przypadku NS-DM przebiega zgodnie

Interwał pomiędzy dwoma kolejnymi chwilami próbkowania wynosi:

Wartość odcinka czasu do chwili pobrania nowej wartości próbki sygnału τp (i + 1) determinuje algorytm MIF [2]:

przy czym: k1, k2 – stałe współczynniki zmiany okresu próbkowania. Poprawna aproksymacja wymaga, aby: k1< 1 < k2; τp0 – startowy odstęp próbkowania, którego wartość jest zawarta w przedziale [ τpmin , τpmax] .

Adaptacja kroku kwantyzacji przebiega według algorytmu MSF [2]:

gdzie: P > 1 – stały współczynnik przyrostu kroku kwantyzacji,

q0 – początkowy krok kwantyzacji.

Zastosowanie w algorytmie ANS-DM mechanizmu powrotu do interwału startowego (4), (5) zwiększa odporność systemu transmisyjnego na zakłócenia oraz gwarantuje uzyskanie synchronizacji po włączeniu odbiornika [3].

Specyfika działania koderów z nierównomiernym próbkowaniem (NS-DM i ANS-DM) nakazuje ich budowę w oparciu o metodę z aproksymacją cyfrową. Przebiegi aproksymujące w postaci krzywych schodkowych, a więc z wybranymi wartościami dyskretnymi, uzyskuje się najczęściej, wykorzystując jako elementy wykonawcze wielobitowe przetworniki c/a. Innym rozwiązaniem jest zastosowanie układów integratorów ładunkowych paczkowych [2, 4]. W tym przypadku stosować można technikę przetwarzania częstotliwość/napięcie, pozwalającą na realizację adaptacji częstotliwości próbkowania, a także kroku kwantyzacji za pomocą tej samej grupy podzespołów cyfrowych [4].

Zapewnienie dużej dynamiki przetwornika NS-DM wymaga stosowania szerokiego zakresu zmian częstotliwości próbkowania.

To z kolei generuje, dużą liczbę jej wartości, niezbędnych podczas procesu kodowania i dekodowania. Konieczność wykonania dużej liczby operacji arytmetyczno-logicznych w czasie rzeczywistym (szczególnie przy wyższych częstotliwościach próbkowania) może być powodem ograniczającym praktyczną realizację przetwarzania w szczególności NS-DM, nawet za pomocą niektórych procesorów sygnałowych. Dlatego stosowane są metody dyskretyzacji wartości interwału próbkowania i kroku kwantyzacji, a także ograniczenia ich liczby do ściśle określonych wartości [5]. Pozwala to na utworzenie tablic odniesień (LookUp Tables) zmniejszających ilość operacji niezbędnych do realizacji procesu przetwarzania nierównomiernego.

Rys. 2. Schemat blokowy modulatora/ demodulatora ANS-DM [6]

W pełni sprzętowe podejście do realizacji kodowania delta, zostało zaprezentowane podglądowo na rys. 2. Modulacji poddawany jest analogowy sygnał wejściowy, a algorytm konwersji jest realizowany sprzętowo. Za obróbkę i aproksymację sygnału analogowego odpowiedzialny jest blok analogowy, natomiast algorytm przetwarzania różnicowego realizowany jest w bloku cyfrowym. Dodatkowo w skład bloku cyfrowego wchodzi moduł odpowiedzialny za sterowanie całym układem oraz system transmisji danych.

Rys. 3. Przykład bardzo prostego cyfrowego układu realizującego dyskretne zmiany wartości częstotliwości próbkowania

W układach tego typu szczególną rolę pełni układ predyktora, którego zadaniem jest wytwarzanie aktualnej wartości sygnału aproksymującego sygnał wejściowy. Bardzo prostą koncepcję układu realizującego dyskretną adaptacyjną zmianę szybkości próbkowania przedstawiono na rys. 3. Ciągła adaptacja częstotliwości próbkowania jest w niej zastąpiona wybranymi wartościami częstotliwości. Selekcji konkretnej częstotliwości dokonuje multiplekser sterowany rewersyjnym układem zliczającym, sprzężonym z algorytmem MIF [2], a wartość chwilowa częstotliwości fs zależy od sekwencji bitów wyjściowych kodera. Częstotliwość fs steruje akumulatorem przetwornika c/a, ustalając ostatecznie kształt krzywej aproksymującej.

W koderze ANS-DM przedstawionym na rys. 4 i 5 zastosowano mechanizm momentalnej adaptacji „wstecz” i 3-bitowy algorytm quasi-koincydencyjny [2] realizowany przez układ logiki adaptacyjnej. Programowalny binarny generator impulsów poza możliwością powrotu do częstotliwości startowej (reset) dokonuje zmian szybkości próbkowania zgodnie z zadanym algorytmem.

Rys. 4. Struktura modulatora ANS-DM z predyktorem w postaci przetwornika c/a oraz cyfrowego akumulatora

Rys. 5. Struktura modulatora ANS-DM z predyktorem w postaci integratora ładunkowego (paczkowego)

Interesującym i konkurencyjnym rozwiązaniem dla predyktora z wielobitowym przetwornikiem c/a jest układ predyktora z integratorem paczkowym (ang. parcelling integrator [3]), którego koncepcja dzięki wykorzystaniu techniki przyrostu ładunku, oddzielnie dla każdego cyklu przetwarzania jest kompatybilna z ideą przetwarzania różnicowego. Pozwala to wyeliminować wielobitowy przetwornik c/a, ograniczając wady, które wnosi on do techniki przetwarzania Δ z adaptacją. W efekcie można uprościć problem kompensacji błędów przesunięcia zera i błędów wzmocnienia, czy ograniczyć błędy nieliniowości całkowej i różniczkowej.

Implementacja predyktora paczkowego w technologii CMOS zaprojektowana i wykonana przez Autorów w technologii AMS 350 nm, zostanie omówiona w dalszej części.

Pierwsze z porównywanych rozwiązań to implementacja bloku predyktora w oparciu o integrator paczkowy w technologii CMOS (AMS 350 nm), będący oryginalnym projektem Autorów artykułu. Został on wykonany praktycznie (rys. 6).

Rys. 6. Schemat blokowy predyktora z wielobitowym przetwornikiem c/a

(bez logiki sterującej)

W celu porównania właściwości dwóch struktur predyktorów dla kodeków ANS-DM, zdecydowano się na realizację predyktora z wielobitowym przetwornikiem c/a, w postaci układu składającego się ze standardowych bloków funkcjonalnych, oferowanych przez dostawców technologii 350 nm do produkcji układów ASIC, jako standardowe podzespoły typu IP core (Intellectual Property core). Dzięki temu można zaprojektować i przeanalizować wiele parametrów takiego predyktora bez jego fizycznej implementacji, jedynie na bazie wyników symulacji przed i po partycjonowaniu technologicznym (symulacje postlayoutowe). Przy założeniu zbliżonej dokładności wykonania i szybkości przetwarzania, możliwe jest porównanie obu rozwiązań pod względem zajmowanej powierzchni, poboru mocy obu struktur koderów czy stopnia komplikacji układów sterowania.

Charakterystyczne cechy przetwarzania nierównomiernego adresowane do przetwarzania sygnału mowy, powodują, że predyktor kodeka ANS-DM, powinien posiadać następujące cechy:

Firma Austria Microsystems (technologia AMS 350 nm [7]), oferuje gotowe podzespoły w postaci makrocel, które pozwalają na realizację predyktora, składającego się z 10-bitowego przetwornika c/a z akumulatorem (rys.6).

Korzystając z tej technologii, projektant ma do dyspozycji gotowe komponenty w postaci makrobloków na poziomie modelu behawioralnego oraz topologii jego realizacji. Podstawowymi elementami jakie można wykorzystać do budowy predyktora są: 10-bitowy przetwornik cyfrowo-analogowy (oznaczany w bibliotece elementów producenta jako DAC10A), układ sterowania składający się z bramek cyfrowych, akumulatora zrealizowanego na bazie 10-bitowego rejestru szeregowo-równoległego (10*JKC1), źródła napięcia referencyjnego (BG05A) oraz wzmacniacza operacyjnego OP05B, służącego jako konwerter prąd/napięcie na wyjściu przetwornika DAC10A [7].

Wybrane parametry podzespołów przedstawiono w tabeli 1.

Tab. 1. Wybrane parametry układów DAC10A, BG05A i OP05B w technologii TECHC35B4C3 produkowanych przez Austria Microsystems:

| UKŁAD | DAC10A | BG05A | OP05B | DF1x10 |

| powierzchnia (mm2) | 0,036 | 0,036 | 0,012 | 0,003 |

| szerokość x (μm) | 167 | 214 | 60,35 | 183 |

| wysokość y (μm) | 214 | 167 | 190 | 16,4 |

| zasilanie (V) | 2,7–3,6 | 3–3,6 | 3–3,6 | 3,3 |

| Wartość1) pobieranego prądu przy zasilaniu 3,3 V (μA) | 330 | 46 | 88 | 0,9 |

| moc (mW) | 1,1 | 0,15 | 0,29 | 0,003 |

| inne | czas ustalania: 100 ns | wartość napięcia referencyjnego: 1.21 V dokładność: 100 ppm | wzmocnienie wzm. z otwartą pętlą: 102 dB, pole wzm.: 2,57 MHz |

1) Wartość prądu określono przy taktowaniu równym 1 MHz

Realizując predyktor ANS-DM z wielobitowym przetwornikiem c/a, przy optymalnym ułożeniu elementów, tak aby znajdowały się obok siebie i bez zbędnych odstępów, uzyskuje się strukturę półprzewodnikową CMOS 350 nm o wymiarach x = 441,35 μm, y =214 μm czyli łącznej powierzchni równej 0,098 mm². Zakładając, że wszystkie komponenty kodera pracują z maksymalną szybkością pobór mocy, liczony jako suma wszystkich składowych wynosi 1,54 mW. Maksymalną częstotliwość pracy przyjęto jako równą 1 MHz.

Implementacja bloku predyktora 1-bitowego, bazująca na integratorze paczkowym w technologii CMOS jest oryginalnym projektem Autorów artykułu.

Działanie bloku predyktora 1- bitowego opiera się na zmianie analogowej wartości wyjściowej o różnicę między aktualną próbką sygnału wejściową a próbką poprzednią. Wartość bieżąca wyjściowa jest modyfikowana o kwant napięcia wynikający z aktualnej rozdzielczości przetwarzania. Taką cechę oprócz układów c/a, w których bieżąca wartość akumulatora może być zmodyfikowana o zadaną wielkość cyfrową, posiadają także sterowane integratory analogowe, a ogólniej układy próbkująco-pamiętające. Najprostszym z nich jest integrator, w którym bieżąca wartość ładunku kondensatora jest modyfikowana przez ładowanie go określoną wartością prądu stałego w zadanym przedziale czasu. Jak udowodniono w pracy [8], tego typu rozwiązanie dobrze sprawdza się w koderach Δ z próbkowaniem równomiernym. Problemy pojawiają się w układach z adaptacją częstotliwości próbkowania. Zmiana wielkości kroku kwantyzacji w koderach delta z próbkowaniem równomiernym wymaga jedynie zmiany prądu ładującego (rozładowującego), integratora. Czas ładowania (rozładowania) w tym przypadku jest wielkością stałą. Takie rozwiązania są stosowne w komercyjnie dostępnych koderach CVSD [6]. Metody tej nie można jednak, bezpośrednio zastosować w koderach z nierównomiernym próbkowaniem, gdyż utrzymanie takiego samego kwantu zamiany napięcia predyktora między kolejnymi chwilami próbkowania wymaga modyfikacji prądu ładowania, adekwatnej do zmiany interwału próbkowania. Jest to zadanie dość proste do rozwiązania układowego, natomiast napotyka liczne problemy implementacyjne w technologii CMOS, związane z zachowaniem symetrii podziału prądów w lustrach kaskodowych, czy symetrii prądu ładowania i rozładowania.

Konstrukcja integratora ładunkowego jest rozwiązaniem, które wykorzystuje ideę pracy układów próbkująco-pamiętających. Istotą jego działania jest sekwencyjna dystrybucja ładunku referencyjnego QRef poprzez układy przenoszące go aż, do kondensatora pamiętającego, który wytwarza napięcie wyjściowe UOUT. Schemat blokowy takiego predyktora (w istocie przetwornika c/a z pamięcią) zamieszczono na rys. 8.

Rys. 7. Schemat blokowy predyktora z 1-bitowym integratorem paczkowym

Rys. 8. Schemat blokowy 1-bitowego predyktora ładunkowego

Proponowany predyktor z integratorem ładunkowym zawiera źródło prądowe IRef, którego wartości są określane przez zewnętrzną rezystancję Rrefzew, pracującą w układzie skompensowanego termicznie źródła napięcia VRef (typu bandgap). Ustalona rezystorem wartość prądu źródła może być jeszcze dzielona w stosunku od 1 do 16 przez podanie na 4-bitowe wejścia sterujące odpowiednich poziomów logicznych (rys. 8). W wykonanej implementacji pozwala to na uzyskiwanie wartości prądu w zakresie od 100 nA do 1,6 μA. Prąd ten (IN) ładuje, albo rozładowuje wewnętrzny kondensator CRef w bloku wytwarzania ładunku referencyjnego +QRef N lub -QRefN. Ładunek ten jest następnie dostarczany do bloku redystrybucji, gdzie powiększa lub zmniejsza wartość sygnału wyjściowego UOUTpredyktora. Przykładowy przebieg czasowy sygnału wyjściowego przedstawiono na rysunku 9.

Rys. 9. Przykładowy oscylogram napięcia UOUT na wyjściu predyktora paczkowego

Interesującą cechą opracowanego rozwiązania jest to, iż wartość napięcia po doładowaniu kondensatora ładunkiem QRef N nie zależy od czasu trwania procesu redystrybucji ładunku, przez co takie rozwiązanie może być zastosowane w koderach delta z nierównomiernym próbkowaniem. Wykonana implementacja predyktora w technologii AMS035, działa poprawnie przy zmianie interwału próbkowania w zakresie od 600 ns do 100 μs, co odpowiada zmianom częstotliwości próbkowania w zakresie od 10 kHz do 1,67 MHz. Layout predyktora z zaznaczonymi najważniejszymi podzespołami przedstawiono na rysunku 10.

Predyktor zajmuje powierzchnię 0,0728 mm2 (400 × 182 μm), pobierając prąd całkowity 261 μA przy napięciu zasilania wynoszącym 3 V, czyli moc pobierana wynosi 783 μW.

Rys. 10. Topografia układu predyktora z integratorem paczkowym

Poprawne działanie predyktora Δ jest uwarunkowane podaniem na jego wejścia sterujące odpowiednich sygnałów cyfrowych. W wersji prototypowej kodera źródłem tych sygnałów, w przypadku obu przedstawionych wcześniej rozwiązań jest układ logiki programowalnej FPGA rodziny Spartan 3E. Zastosowanie takiego samego układu w obu przypadkach, pozwala na porównanie użytych zasobów sprzętowych potrzebnych do kontroli pracy każdego z predyktorów w konkretnej realizacji kodera ANS-DM.

Opis działania logiki sterującej oboma predyktorami wykonano w języku VHDL. Każda z realizacji składa się z dwóch sekcji adaptacji: kroku kwantyzacji i adaptacji interwału próbkowania. Zadaniem pierwszej jest podawanie ustalonej wartości q, przy czym zwykle możliwe są dwa podejścia realizacji samego mechanizmu adaptacji. Pierwsza polega na obliczeniu kroku kwantyzacji w chwili adaptacji (na podstawie sygnałów zewnętrznych, pochodzących z bloku implementującego funkcję MSF [2]) oraz bieżącej wartości kroku. Druga metoda zakłada z góry ustalone wartości kroków kwantyzacji wpisane w tablicy LUT1. Na podstawie sygnałów zewnętrznych modyfikowany jest jedynie wskaźnik bieżącego pola w tej tablicy. Z uwagi na naturalne stosowanie tablic LUT w syntezie kodu VHDL oraz minimalizację obliczeń zdecydowano się na drugie rozwiązanie. W przypadku modyfikacji interwału próbkowania możliwe jest takie samo podejście, ale w tym przypadku wskaźnik do tablicy LUT2 jest obliczany na bazie implementacji funkcji MIF [2], a sama tablica zawiera odstępy między kolejnymi chwilami próbkowania. Porównując wyniki syntezy logicznej bloków sterowania predyktorem z integratorem paczkowym oraz wielobitowym przetwornikiem c/a widać, iż również pod tym względem konstrukcja predyktora ładunkowego wymaga zasobów logiki sterowania (około 40%).

Tab. 2. Zestawienie wyników syntezy logicznej układów sterujących kodera ANS-DM implementowanego w układzie Spartan 3E FPGA

| Rodzaje użytych zasobów | Dostępne zasoby układu Spartan | Logika sterowania układem predyktora z integratorem paczkowym | Logika sterowania układem predyktora z wielobitowym przetwornikiem c/a | ||

| wykorzystano | [ % ] | wykorzystano | [ % ] | ||

| Number of Slice Flip Flops | 9 312 | 106 | 1, 138% | 169 | 1,815% |

| Number of 4 input LUTs | 9 312 | 227 | 2, 438% | 296 | 3,179% |

| Number of occupied Slices | 4 656 | 148 | 3, 179% | 203 | 4,359% |

| Number of Slices containing only related logic | 423 | 148 | 34, 99% | 203 | 47,990% |

| Total Number of 4 input LUTs | 9312 | 266 | 2, 856% | 348 | 3,737% |

W artykule porównano dwie implementacje predyktora (podstawowego bloku funkcjonalnego kodera delta z adaptacją interwału próbkowania) jednej opartej o wielobitowy przetwornik c/a i drugiej z integratorem paczkowym obie bazujące na technologii CMOS.

Zestawiając wyznaczone parametry dotyczące możliwości realizacji obu predyktorów w postaci scalonej można stwierdzić, iż powierzchnia predyktora z integratorem paczkowym stanowi 74% powierzchni układu skonstruowanego z gotowych podzespołów i opartego o wielobitowy przetwornik c/a. Średnia wielkość mocy pobierana przez predyktor z integratorem paczkowym stanowi jednak 51% poboru mocy układu przetwornikiem wielobitowym c/a, co jest kluczowym czynnikiem przemawiającym na korzyść proponowanego przez autorów rozwiązania.

Zachęcające są również wyniki syntezy logicznej bloków sterowania predyktorem z integratorem paczkowym. Wskazują one na około 40% zysk w wyniku stosowania 1-bitowego integratora ładunkowego.

Można przyjąć, że wykonanie kodera ANS-DM w tej technologii CMOS 350 nm, pozwala na osiągnięcie zbliżonych parametrów dynamicznych w obydwu rodzajach rozwiązań układowych predyktorów. Potwierdzają to parametry katalogowe AustriaMicrosystems i pomiary szybkości predyktora paczkowego zrealizowanego w postaci układu ASIC.

Przedstawiona w artykule analiza pozwala stwierdzić, iż rozwiązanie kodera ANS-DM z predyktorem paczkowym jest konkurencyjne wobec stosowanych dotychczas rozwiązań, zajmując mniejszą powierzchnię, zużywając mniej energii. Wymaga ponadto mniejszej liczby bloków logicznych w układzie sterowania.

Uzyskany wynik porównania kilku ważnych parametrów koderów ANS-DM potwierdza słuszność stosowania w technologii CMOS koncepcji predyktorów opartych o metodę przyrostową, a nie metodę przetwarzania bezwzględnej wartości sygnału czyli o przetwornik c/a wielobitowy. Jednak szczegółowego porównania wszystkich parametrów przetwarzania, można będzie dokonać dopiero po wykonaniu predyktora z przetwornikiem wielobitowym c/a w technologii CMOS 350 nm i dokonaniu stosownych pomiarów.

Literatura:

[1] Miśkowicz M., Golański R.: LON Technology in Wireless Sensor Networking Applications. SENSORS, Special Issue: Wireless Sensor Networks and Platforms, vol. 6, 2006, pp. 30–48; http://www.mdpi. org/sensors/papers/s6010030.pdf .

[2] Zhu Y.S., Leung S.W., Wong C.M.: Adaptive nonuniform sampling delta modulation for audio/image processing. IEEE Trans. On Consumer Electronic, vol. 42, No.4, 1996, 1062–1072.

[3] Golański R.: Study on the dynamic range of delta modulations with time-varying sampling periods. IEEE Signal Processing Letters, vol. 11, No. 8, 2004, 666–670.

[4] Tewksbury S. K.: Discrete Adaptive Delta Modulation system. United States Patent 3,815, 033, 1974.

[5] Golański R., Kołodziej J., Kuta S.: Non-uniform Sampling Delta Modulation- Principles of Parameters Design, WSEAS TRANSACTIONS on CIRCUITS and SYSTEMS, Issue 12, Volume 8, December 2009.

[6] Golański R.: 1-bitowe przetworniki a/c i c/a z próbkowaniem adaptacyjnym-metody analizy i ocena właściwości”, Seria: Rozprawy, Monografie Nr 151, AGH Uczelniane Wydawnictwa Naukowo - Dydaktyczne, Kraków 2005.

[7] Austria Microsystems - www.asic.austriamicrosystems.com,

[8] Kołodziej J.: Układowe realizacje jednobitowych przetworników delta z adaptacją częstotliwości próbkowania, Rozprawa doktorska, Katedra Elektroniki AGH, Kraków 2007.

| REKLAMA |

| REKLAMA |