W projektowaniu systemu wykorzystany został szereg narzędzi programistycznych. Pierwszym z nich jest ISE 10.1.3, przy użyciu którego zbudowano opis z wykorzystaniem języka VHDL, systemu opartego na mikroprocesorze PicoBlaze. Środowisko EDK 10.1.3 posłużyło do stworzenia systemu z procesorami MicroBlaze. Dodatkowo posiada ono moduł wspomagający tworzenie oprogramowania SDK (Software Development Kit), który posłużył do napisania aplikacji szyfrującej dane otrzymywane poprzez interfejs RS232. Program dla procesorów PicoBlaze powstał z użyciem środowiska pBlazeIDE 3.7.4, które poza kompilatorem asemblera, posiada rozbudowany debuger.

Rys. 6. Wykorzystana platforma testowa [10] |

W celu weryfikacji poprawności działania projektów w rzeczywistym systemie wykorzystane zostało

Testy przeprowadzono z użyciem płytki uruchomieniowej firmy AVNET AES-V5FXT-EVL30-G, zbudowanej na układzie FPGA Virtex 5 FX 30T firmy Xilinx (rys. 6.) Do układu doprowadzono sygnał zegarowy z oscylatora o częstotliwości 100 MHz. Płyta wyposażona jest w dwa interfejsy szeregowe (jeden z konwerterem USB – RS232), które posłużyły do transmisji przetwarzanych danych.narzędzie ChipScope Pro, które rejestruje przebiegi wewnątrz układu w czasie pracy umożliwiając w ten sposób określenie szybkości przetwarzania.

W tabeli 1. umieszczone zostało zestawienie liczby wymaganych zasobów przez dwie zaproponowane konfigurację oraz ich procentowy udział w odniesieniu do dostępnych w wykorzystywanym układzie FPGA.

Tabela 1: Zestawienie liczby wymaganych zasobów przez zaproponowane konfiguracje

| Rodzaj zasobów | MultiMicroBlaze | MultiPicoBlaze | Dostępne zasoby | ||

| Liczba | Udział | Liczba | Udział | ||

| Flip-Flop | 3282 | 16% | 808 | 4% | 20480 |

| LUT | 7017 | 34% | 1123 | 5% | 20480 |

| FPGA slice | 2224 | 43% | 475 | 9% | 5120 |

| BlokRAM | 40 | 59% | 5 | 7% | 68 |

System oparty na procesorach MicroBlaze wykorzystuje cztery razy więcej zasobów logicznych, co jest zasadne z uwagi na 32-bitową jednostkę ALU w odniesieniu do 8-bitowej w procesorze PicoBlaze. Wykorzystanie pamięci jest ośmiokrotnie większe, nie jest możliwe zmniejszenie obszaru pamięci ze względu na to, że minimum wymagane dla jednego procesora wynosi ok. 10 kB. Dla systemu z procesorem PicoBlaze jest to 2560 B dla każdego procesora. Prostsza architektura umożliwia również taktowanie systemu MultiPicoBlaze z zegarem 200 MHz wytworzonym z wykorzystaniem dostępnej pętli PLL, w przeciwieństwie do 100 MHz dla architektury z procesorami MicroBlaze. Rysunek 7 pozwala na porównanie wielkości systemów w obrębie układu FPGA.

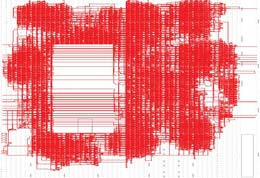

a) a) |  b) b) |

| Rys. 7. Rozplanowanie sieci połączeń w obrębie układu FPGA; a) MultiPicoBlaze, b) MultiMicroBlaze | |

|

|

| REKLAMA |

| REKLAMA |